# Grain Size and Interface Dependence of Bias Stress Stability of n-Type Organic Field Effect Transistors

Rizwan Ahmed,\*,\*,\* Clemens Simbrunner,\*,\* M. A. Baig,\* and H. Sitter

ABSTRACT: The effect of grain size and interface dependence of bias stress stability of C<sub>60</sub>-based n-type organic field effect transistors (OFETs) has been studied. It has been realized that, with increasing grain size of C<sub>60</sub>, the bias stress induced threshold voltage shift can be controlled and this effect is mainly attributed to the mechanism of charge trapping at grain boundaries. It is further studied that the growth of C<sub>60</sub> on the surface of parylene at elevated substrate temperature leads to the creation of radicals at the interface between the active layer and the gate dielectric. These radicals help to improve the bias stress stability of C<sub>60</sub>-based n-type OFETs. For achieving the bias stress stability, we have presented a procedure of creation of radicals at the interface between C<sub>60</sub> and parylene in single gate OFETs instead of dual gate OFETs.

KEYWORDS:  $C_{60}$  bias stress, n-type OFETs stability, threshold voltage shift, charge trapping in semiconductor and dielectric interface, grain boundaries, parylene

## 1. INTRODUCTION

Potentials for the uses of organic semiconductors in large area devices, such as light emitting diodes, drivers for flexible display, <sup>2</sup> organic solar cells, <sup>3</sup> photodetectors, <sup>4</sup> and identification tags made them interesting for researchers to improve their performance.<sup>5</sup> The main factors which can aggravate the performance of the organic field effect transistors (OFETs) are the low charge carrier field effect mobility,6 environmental stability,<sup>7,8</sup> and bias stress reliability.<sup>9,10</sup> The major hindrances in overcoming these inhibiting factors are the poor knowledge of charge transport in organic semiconductors and the nature of degradation mechanisms under bias stress and in ambient environment. A strong improvement in the knowledge of these obstacles is a primary key in the optimization of the performance of OFETs. The operation of OFETs relys on the charge injection at source drain contacts, <sup>11</sup> the degree of crystallinity of the active layer, <sup>12–14</sup> and the interface between the dielectric and the organic semiconductor layer. 15 According to the aspect of electronic circuit design, besides the high charge carrier mobility, reliability of OFETs is an important issue. Already some efforts have been made to perform reliable studies of p-type and n-type OFETs. 16-19 The bias stress stability of p-type OFETs was measured, 20 and it was inferred that the barrier height for charge trapping can be controlled by using self-aasembled monolayers (SAMs) on the surface of the gate dielectric. It was reported that increasing the barrier height for charge trapping can decrease the bias stress effects. It was observed that the charge trapping also has some dependence on the surface morphology of the active layer. The bias stress effect in pentacene OFETs was studied with different dielectrics.<sup>21</sup> It was reported that the fabrication of devices stable against bias stress is possible by using appropriate gate dielectric layers. The trapped charges were visualized in real time using scanning Kelvin probe microscopy (SKPM)<sup>22</sup> and it was reported that the charges are trapped at the surface of the gate dielectric, instead of the semiconducting layer.

In a recent article, the bias stress effects on C<sub>60</sub> based n-type OFETs have been discussed comprehensively. The experimental results reveal that, during the bias stress, the charges can be trapped in the organic semiconductor as well as in the gate insulator layers. The bias stress induced charge trapping is 10 times faster in the active layers as compared to the gate insulator layer. The charge trapping in the active layer can be controlled by depositing the organic semiconductors at elevated substrate temperatures, while the selection of an appropriate gate insulator can also decrease the bias stress effects up to 55%.<sup>23</sup> From the literature, it can be easily deduced that during bias stress the charges can be trapped in the active layer, in the gate dielectric, or at the interface between gate dielectric and organic semiconductor and these trapped charges induce a threshold voltage shift.<sup>24,25</sup>

In our recent article,<sup>26</sup> it was reported that dual gate OFETs are more stable against bias stress as compared to single gate OFETs. However, fabrication of dual gate OFETs is

Received: July 10, 2015 Accepted: September 18, 2015 Published: September 18, 2015

<sup>&</sup>lt;sup>†</sup>Institute of Semiconductor and Solid State Physics, Johannes Kepler University, A-4040 Linz, Austria

<sup>\*</sup>National Centre for Physics, Quaid-e-Azam University Campus, 440000 Islamabad, Pakistan

<sup>§</sup>Institute of Solid State Physics, University of Bremen, D-28359 Bremen, Germany

**ACS Applied Materials & Interfaces**

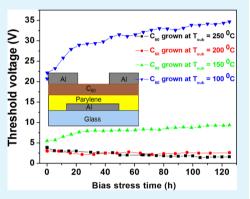

Figure 1. Transfer characteristics measured before bias stress, after 24 h of bias stress, and after 125 h of bias stress time with  $C_{60}$  grown at (a)  $T_{\text{sub}} = 100 \,^{\circ}\text{C}$ , (b)  $T_{\text{sub}} = 150 \,^{\circ}\text{C}$ , (c)  $T_{\text{sub}} = 200 \,^{\circ}\text{C}$ , and (d)  $T_{\text{sub}} = 250 \,^{\circ}\text{C}$ .

complicated as compared with single gate OFTEs and it also requires additional experimental efforts. The main concealed feature of dual gate OFETs which is responsible for the bias stress stability is the modified interface due to the formation of radicals.<sup>27</sup> In the present work, we have demonstrated that these radicals which are responsible for the stability of OFETs against bias stress can be created in single gate OFETs. Therefore, the bias stress stability of OFETs in more simple geometrical structures can be achieved.

## 2. EXPERIMENTAL DETAILS

The experimental procedure for the fabrication of OFETs was almost the same as that used in our previous studies. 23,28 The OFETs were fabricated by using glass substrates. Before the fabrication of OFETs, the glass substrates were cleaned using acetone and deionized water in an ultrasonic bath and dried in a nitrogen flow. The gate electrode having a thickness of 100 nm and a width 0.5 mm was evaporated by using a shadow mask in a vacuum of 10<sup>-6</sup> mbar. The parylene layer as gate dielectric was deposited on the surface of the gate electrode using a homemade parylene evaporation system which works with a threezone process. In the first zone the parylene was evaporated at 100 °C. In the second zone the parylene vapor has to pass through a high temperature zone (750 °C), where pyrolysis leads to a cleavage of the dimers. In the last zone the monomers are deposited on the surface of the gate electrode at room temperature. For the fabrication of OFETs, 1  $\mu$ m thick parylene layers were deposited as the gate dielectric. A 200 nm thick layer of  $C_{60}$  (MER Corp.) was deposited by hot wall epitaxy (HWE) in a vacuum of  $10^{-6}$  mbar with different substrate temperatures  $T_{\rm sub}$  = 100, 150, 200, and 250 °C, a source temperature of  $T_{\rm s}$  = 360 °C, and a wall temperature of  $T_{\rm wall}$  = 400 °C. For top contact electrodes, 70 nm thick Al was evaporated under high vacuum  $(10^{-6} \text{ mbar})$ , using a shadow mask. The channel length L and width W in the OFETs were 70  $\mu m$  and 1.5 mm, respectively. After the evaporation of C<sub>60</sub> in the HWE reactor, the device was transported to

the glovebox in ambient conditions. All the measurements were performed inside the glovebox in a nitrogen controlled environment. The gate voltage was applied by a Keithley 6487 Pico-Ampere meter, and the same was used for measuring the leakage current and the transfer characteristics. The source—drain voltage was applied by a Keithley 2400 voltage source unit, and the same was used for monitoring the output characteristics. For applying the bias stress, the source—drain voltage was varied from 0 to 50 V and the gate—source voltage was varied from —10 to +50 V. All the measurements were automatically controlled by a computer switch, and all experimental data points were registered by a Metlab program.

## 3. RESULTS AND DISCUSSION

For the fabrication of OFETs, the growth of  $C_{60}$  active layers was done by the HWE system. The HWE system has three ovens, named the source oven, wall oven, and substrate oven. The source oven was used to evaporate the organic material  $(C_{60})$  and the wall oven was used to avoid unnecessary depositions on the walls of the tube between source and substrate, while the substrate oven was used to control the surface mobility of the impinging molecules and in that way the morphology of the deposited material. Therefore, in an HWE system, it was possible to vary the grain size and crystallinity of the film by varying the substrate temperature.  $C_{60}$  was grown at four different substrate temperatures  $(T_{sub})$  of 100, 150, 200, and 250 °C. The bottom gate top contact OFETs were fabricated with four different morphologies of the active layer while keeping the dielectric layer the same (parylene with capacitance density  $1.77 \times 10^{-9}$  F/cm<sup>2</sup>). The four OFETs, fabricated with C<sub>60</sub> grown at four different substrate temperatures, were installed in the measurement setup for applying bias stress. The continuous bias stress was applied for 125 h to each device, and the transfer characteristics were registered. The transfer characteristics measured before bias stress, after 24 h of bias stress, and after 125 h of bias stress are presented in the Figure 1. The atomic force microscopic (AFM) images of C<sub>60</sub> grown at different substrate temperatures are also presented as insets in the corresponding device characteristics. It is quite evident from the AFM images that the grain size in the C<sub>60</sub> layer increases as the substrate temperature increases. The structural analysis of the C<sub>60</sub> layers deposited at different substrate temperatures depicts that the crystallinity can be improved by depositing C<sub>60</sub> layers at elevated substrate temperatures.<sup>29</sup> Figure 1 clearly illustrates that the devices fabricated with C<sub>60</sub> layers grown at elevated substrate temperatures show better performance as compared to the devices fabricated with C<sub>60</sub> layers grown at lower substrate temperatures. The bias stress stability of OFETs is a major issue. 10 The transfer characteristic measured after 24 h of bias stress is shifted toward the transfer characteristic measured after 125 h of bias stress time. This means that, in the initial hours of continuous bias stress, it shifts rapidly and then slowly reaches a saturated value. The shift in the transfer characteristic can be attributed to the bias stress induced threshold voltage shift. The threshold voltage was measured for the whole period of investigation and is presented in Figure 2 along with a

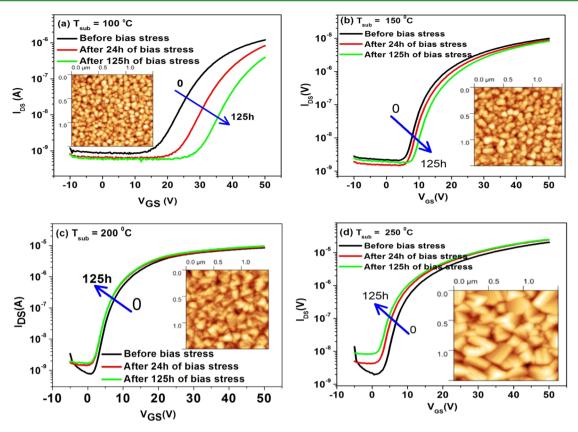

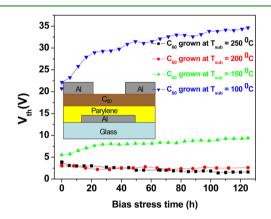

Figure 2. Threshold voltage shift with bias stress time.

geometrical sketch of the OFET as an inset. During the entire period of investigations, the threshold voltage was stable in the OFETs fabricated with  $C_{60}$  grown at substrate temperatures of 200 and 250 °C, while the OFETs fabricated with  $C_{60}$  grown at substrate temperatures of 100 and 150 °C, show a shift in the threshold voltage. It is worth noting that the direction of threshold voltage shift in the OFETs fabricated with  $C_{60}$  layers grown at  $T_{\rm sub} = 200$  and 250 °C is opposite that for the devices fabricated at lower  $T_{\rm sub} = 100$  and 150 °C.

fabricated at lower  $T_{\rm sub}=100$  and 150 °C. In a recent article,  $^{23}$  it has been reported that increasing the grain size or decreasing the grain boundaries within the OFET channel improves the stability of the threshold voltage against bias stress. The threshold voltage shift measured in the devices fabricated at  $T_{\rm sub}=100$  and 150 °C is in good agreement with earlier reports, but the threshold voltage shifts observed in the devices fabricated with active layer grown at  $T_{\rm sub}=200$  and 250 °C are not in line with the previous reports. It is evident from Figure 2 that the threshold voltage shift in the OFETs fabricated with  $C_{60}$  grown at higher substrate temperature ( $T_{\rm sub}=250$  °C) has larger values compared to the OFETs fabricated at lower substrate temperature ( $T_{\rm sub}=200$  °C), which is contrary to our earlier results. The electron trapping is

believed to be the main reason for the shift in the threshold voltage in n-type OFETs.<sup>30</sup> A similar type of threshold voltage shift to more positive  $V_{GS}$  has been already reported for another n-type organic semiconductor, namely, perylene diimide derivative PTCDI- $C_{13}H_{27}$ . In the present work, the parylene was used as a gate dielectric. The reactivity of  $C_{60}$  and parylene can be found in the literature.<sup>32</sup> Furthermore, it has been already reported that the evaporation of parylene on  $C_{60}$  layers can create radicals and the formation of a clean interface (free of radicals) between the active layer and the gate dielectric is only possible by depositing  $C_{60}$  layers on the surface of parylene but not vice versa. Therefore, the creation of such radicals is reported in top-gate bottom-contact OFETs but not in bottom-gate top-contact OFETs. It has been discussed in detail that the presence of these radicals at the interface between C<sub>60</sub> and parylene can cause the bias stress induced threshold voltage shift to more negative  $V_{\rm GS}$ . <sup>26</sup>

In the fabrication process of bottom-gate OFETs, the parylene monomers evaporated at 100 °C through the high temperature zone (750 °C) to the deposition chamber held at room temperature and polymerize at the surface of the glass substrate. After the pyrolysis, the conformal thin parylene films are thermally stable up to 200 °C. 33 Therefore, if we treat the parylene thin films around 200 °C or higher, then there is a finite probability that cross-linked dimers can reopen their side chains or become thermally activated. Consequently, while deposition of C<sub>60</sub> on the surface of parylene at a substrate temperature around 200 °C or higher, there is a finite probability that the thermally activated parylene monomers may react with C<sub>60</sub> instead of polymerize with each other. The reactivity of C<sub>60</sub> with parylene can create radicals, <sup>27</sup> and these radicals can cause the bias stress induced threshold voltage shift toward the more negative  $V_{\rm GS}$ . The threshold voltage shift toward the more negative  $V_{\rm GS}$  in the OFETs fabricated with active layers grown at substrate temperatures of 200 and 250 °C confirms our assertion that the radicals are formed at the interface. Therefore, the threshold voltage shift toward the more negative  $V_{GS}$  can be attributed to the creation of radicals at the C<sub>60</sub> and parylene interface and our present study is in good agreement with the earlier reports.<sup>26,3</sup>

Besides the bidirectional threshold voltage shift in our device, it was also observed that the threshold voltage shift in the OFET fabricated at  $T_{\text{sub}} = 150 \,^{\circ}\text{C}$  is less compared to that in the OFET fabricated at  $T_{\text{sub}}$  = 100 °C. The parylene thin film is thermally stable up to 200 °C; therefore, this reduction cannot be associated with the creation of radicals at the interface between the C<sub>60</sub> and parylene. However, this reduction in the value of bias stress induced threshold voltage shift is related to the grain boundaries.<sup>23</sup> From the AFM images, it is also obvious that the grain size of  $C_{60}$  increases with the increase of substrate temperature during the growth of active layers. The OFETs fabricated with C<sub>60</sub> grown at higher substrate temperatures (200, 250  $^{\circ}\text{C})$  have a larger grain size of  $\text{C}_{60}$  as compared to the OFETs fabricated with C<sub>60</sub> grown at lower substrate temperatures (100, 150 °C). The decrease in the bias stress induced threshold voltage shift with an increase in the grain size of C<sub>60</sub> is quite evident from Figure 1a,b. The experimental results reveal that increasing the grain size or decreasing the grain boundaries within the OFET channel improves the bias stress stability of OFETs. Therefore, it is very hard to exclude the correlation of grain size with the threshold voltage shift in the OFETs fabricated with C<sub>60</sub> grown at higher substrate temperatures (200, 250 °C), having the larger grain size as

compared to the  $C_{60}$  grown at substrate temperatures (100, 150 °C). In other words, the bias stress stability, observed in the OFETs fabricated with active layer grown at  $T_{\rm sub} = 200$  °C, can be conceived as the combined effect of grain boundaries<sup>23</sup> as well as the creation of radicals at the interface between the active layer and gate dielectric.<sup>26,27</sup>

The creation of radials in the single gate devices provides us several benefits: (1) For achieving bias stress stability, the number of experimental steps are decreased and stability of on/off ratio is improved (see Figure 1c) as compared to dual gate OFETs.  $^{26}$  (2) By combining the effect of grain boundaries and creation of radicals, it is possible to decrease the temperature of the growth of the active layer from 250 to 200 °C for threshold voltage stability,  $^{23}$  which will provide us an opportunity to fabricate OFETs on plastic/flexible substrates.  $^{2}$  (3) Threshold voltage stability in  $C_{60}$ -based OFETs can be achieved with low price dielectric (parylene) layers instead of high price dielectric (benzocyclobutene (BCB), etc.).  $^{23}$  All these benefits are helpful in decreasing the cost of fabrication of  $C_{60}$ -based OFETs.

#### 4. CONCLUSION

In summary, the effect of grain size and interface dependence of bias stress stability of  $C_{60}$ -based n-type OFETs is reported. It is shown that, by increasing the grain size of  $C_{60}$ , the bias stress induced threshold voltage shift can be controlled and this effect is mainly attributed to the mechanism of charge trapping related to the grain boundaries. It is also found that the growth of  $C_{60}$  on the surface of parylene at higher substrate temperatures (200, 250 °C) leads toward the creation of radicals at the interface between the active layer and the gate dielectric. These radicals can help in improving the bias stress stability of  $C_{60}$ -based n-type OFETs. For the bias stress stability, we have presented a procedure of creation of radicals at the interface between the  $C_{60}$  and parylene in single gate OFETs instead of dual gate OFETs.

## AUTHOR INFORMATION

#### **Corresponding Author**

\*E-mail: riz.phy@gmail.com or rizwan.ahmed@ncp.edu.pk.

# Notes

The authors declare no competing financial interest.

## REFERENCES

- (1) Li, G.; Zhao, Y.; Li, J.; Cao, J.; Zhu, J.; Sun, X. W.; Zhang, Q. Synthesis, Characterization, Physical Properties, and OLED Application of Single BN-Fused Perylene Diimide. *J. Org. Chem.* **2015**, *80*, 196–203.

- (2) Nigam, A.; Schwabegger, G.; Ullah, M.; Ahmed, R.; Fishchuk, I. I.; Kadashchuk, A.; Simbrunner, C.; Sitter, H.; Premaratne, M.; Rao, V. R. Strain Induced Anisotropic Effect on Electron Mobility in C<sub>60</sub> Based Organic Field Effect Transistors. *Appl. Phys. Lett.* **2012**, *101*, 083305.

- (3) Chen, W.; Yang, X.; Long, G.; Wan, X.; Chen, Y.; Zhang, Q. A Perylene Diimide (PDI)-Based Small Molecule with Tetrahedral Configuration as a non-Fullerene Acceptor for Organic Solar Cells. *J. Mater. Chem. C* **2015**, *3*, 4698–4705.

- (4) Nie, R.; Wang, Y.; Deng, X. Aligned Nanofibers as an Interfacial Layer for Achieving High-Detectivity and Fast-Response Organic Photodetectors. ACS Appl. Mater. Interfaces 2014, 6, 7032–7037.

- (5) Li, J.; Zhang, Q. Linearly Fused Azaacenes: Novel Approaches and New Applications Beyond Field-Effect Transistors (FETs). ACS Appl. Mater. Interfaces 2015, DOI: 10.1021/acsami.5b00113.

- (6) Nigam, A.; Schwabegger, G.; Ullah, M.; Ahmed, R.; Fishchuk, I. I.; Kadashchuk, A.; Simbrunner, C.; Sitter, H.; Premaratne, M.; Rao, V. R. Anisotropic Strain Effect On Electron Transport In C<sub>60</sub> Organic

- Field Effect Transistors. MRS Online Proc. Libr. 2013, 1501, No. mrsf12-1501-p07-05.

- (7) Wang, C.; Zhang, J.; Long, G.; Aratani, N.; Yamada, H.; Zhao, Y.; Zhang, Q. Synthesis, Structure, and Air-stable N-type Field-Effect Transistor Behaviors of Functionalized Octaazanonacene-8,19-dione. *Angew. Chem., Int. Ed.* **2015**, *54*, 6292–6296.

- (8) Ahmed, R.; Simbrunner, C.; Schwabegger, G.; Baig, M. A.; Sitter, H. Air Stability of C<sub>60</sub> Based N-Type OFETs. *Synth. Met.* **2014**, *188*, 136–139

- (9) Lee, W. H.; Choi, H. H.; Kim, D. H.; Cho, K. Microstructure Dependent Bias Stability of Organic Transistors. *Adv. Mater.* **2014**, *26*, 1660–1680.

- (10) Sirringhaus, H. Reliability of Organic Field-Effect Transistors. *Adv. Mater.* **2009**, *21*, 3859–3873.

- (11) Ahmed, R.; Simbrunner, C.; Schwabegger, G.; Baig, M. A.; Sitter, H. The Role of Metal Contacts in The Stability of N-Type Organic Field Effect Transistors. *Appl. Phys. A: Mater. Sci. Process.* **2014**, *117*, 2235–2240.

- (12) Chou, W.; Cheng, H. An Orientation-Controlled Pentacene Film Aligned by Photoaligned Polyimide for Organic Thin-Film Transistor Applications. *Adv. Funct. Mater.* **2004**, *14*, 811–815.

- (13) Bolognesi, A.; Berliocchi, M.; Manenti, M.; Di Carlo, A.; Lugli, P.; Lmimouni, K.; Dufour, C. Effects of Grain Boundaries, Field-Dependent Mobility, and Iinterface Trap States on The Electrical Characteristics of Pentacene TFT. *IEEE Trans. Electron Devices* **2004**, *51*, 1997–2003.

- (14) Di Carlo, A.; Piacenza, F.; Bolognesi, A.; Stadlober, B.; Maresch, H. Influence Of Grain Sizes On The Mobility Of Organic Thin-Film Transistors. *Appl. Phys. Lett.* **2005**, *86*, 263501.

- (15) Klauk, H.; Halik, M.; Zschieschang, U.; Schmid, G.; Radlik, W.; Weber, W. High-Mobility Polymer Gate Dielectric Pentacene Thin Film Transistors. *J. Appl. Phys.* **2002**, *92*, 5259–5263.

- (16) Hwang, D. K.; Fuentes-Hernandez, C.; Kim, J.; Potscavage, W. J., Jr.; Kim, S.-J.; Kippelen, B. Top-Gate Organic Field-Effect Transistors With High Environmental And Operational Stability. *Adv. Mater.* **2011**, *23*, 1293–1298.

- (17) Ahmed, R.; Sams, M.; Simbrunner, C.; Ullah, M.; Rehman, K.; Schwabegger, G.; Sitter, H.; Ostermann, T. Reproducibility and Stability of C<sub>60</sub> Based Organic Field Effect Transistor. *Synth. Met.* **2012**, *161*, 2562–2565.

- (18) Luo, X.; Du, L.; Yao, B.; Lv, W.; Sun, L.; Li, Y.; Wu, Z.; Wen, Z.; Peng, Y. Operational Dynamics and Architecture Dependence of Double-gate OFETs With Balanced Top and Bottom Channel Characteristics. *J. Mater. Chem. C* **2015**, *3*, 7336–7344.

- (19) Ahmed, R.; Simbrunner, C.; Schwabegger, G.; Baig, M. A.; Sitter, H. Stability Of Low Voltage N-Type Organic Field Effect Transistors. *Synth. Met.* **2014**, *197*, 18–22.

- (20) Miyadera, T.; Wang, S. D.; Minari, T.; Tsukagoshi, K.; Aoyagi, Y. Charge Trapping Induced Current Instability in Pentacene Thin Film Transistors: Trapping Barrier And Effect Of Surface Treatment. *Appl. Phys. Lett.* **2008**, *93*, 033304–033306.

- (21) Häusermann, R.; Batlogg, B. Gate Bias Stress In Pentacene Field-Effect-Transistors: Charge Trapping In The Dielectric Or Semiconductor. *Appl. Phys. Lett.* **2011**, *99*, 083303.

- (22) Mathijssen, S. G. J.; Kemerink, M.; Sharma, A.; Cölle, M.; Bobbert, P. A.; Janssen, R. A. J.; de Leeuw, D. M. Charge Trapping At The Dielectric Of Organic Transistors Visualized In Real Time And Space. *Adv. Mater.* **2008**, *20*, 975–979.

- (23) Ahmed, R.; Simbrunner, C.; Schwabegger, G.; Baig, M. A.; Sitter, H. Ameliorating the bias stress stability of n-type OFETs. *Org. Electron.* **2014**, *15*, 3203–3210.

- (24) Street, R. A.; Salleo, A.; Chabinyc, M. L. Bipolaron Mechanism For Bias-Stress Effects In Polymer Transistors. *Phys. Rev. B: Condens. Matter Mater. Phys.* **2003**, *68*, 85316.

- (25) Sharma, A.; Mathijssen, S.; Smits, E.; kemerink, M.; de Leeuw, D.; Bobbert, P. Proton Migration Mechanism For Operational Instabilities In Organic Field-Effect Transistors. *Phys. Rev. B: Condens. Matter Mater. Phys.* **2010**, 82, 75322.

- (26) Ahmed, R.; Kadashchuk, A.; Simbrunner, C.; Schwabegger, G.; Baig, M. A.; Sitter, H. Geometrical Structure And Interface Dependence Of Bias Stress Induced Threshold Voltage Shift In C<sub>60</sub> Based OFETs. ACS Appl. Mater. Interfaces 2014, 6, 15148–15153.

- (27) Ahmed, R.; Kadashchuk, A.; Simbrunner, C.; Schwabegger, G.; Havlicek, M.; Głowacki, E.; Sariciftci, N. S.; Baig, M. A.; Sitter, H. Photosensitivity of Top Gate C<sub>60</sub> Based OFETs: Potential Applications for High Efficiency Organic Photodetector. *Org. Electron.* **2014**, *15*, 175–181.

- (28) Schwabegger, G.; Ullah, M.; Irimia-Vladu, M.; Baumgartner, M.; Kanbur, Y.; Ahmed, R.; Stadler, P.; Bauer, S.; Sariciftci, N. S.; Sitter, H. High Mobility, Low Voltage Operating  $C_{60}$  Based N-Type Organic Field Effect Transistors. *Synth. Met.* **2011**, *161*, 2058–2062.

- (29) Montaigne Ramil, A. M.; Singh, Th.B.; Haber, N. T.; Marjanovic, N.; Gunes, S.; Andreev, A.; Matt, G. J.; Resel, R.; Sitter, H.; Sariciftci, N. S. Influence Of Film Growth Conditions On Carrier Mobility Of Hot Wall Epitaxially Grown Fullerene Based Transistors. *J. Cryst. Growth* **2006**, 288, 123–127.

- (30) Chua, L. L.; Zaumseil, J.; Chang, J. F.; Ou, E.; Ho, P.; Sirringhaus, H.; Friend, R. H. General Observation Of N-Type Field-Effect Behaviour In Organic Semiconductors. *Nature* **2005**, *434*, 194–199

- (31) Debucquoy, M.; Rockele, M.; Genoe, J.; Gelinck, G. H.; Heremans, P. Charge Trapping In Organic Transistor Memories: On The Role Of Electrons And Holes. *Org. Electron.* **2009**, *10*, 1252–1258

- (32) Loy, D. A.; Assink, R. A. Synthesis Of A Fullerene  $C_{60}$ -P-Xylylene Copolymer. J. Am. Chem. Soc. **1992**, 114, 3977–3978.

- (33) V&P Scientific, Inc., home page. http://www.vp-scientific.com/parylene properties.htm (accessed Sept 19, 2015).